- Laut Sandisk wird der 3D -Matrixspeicher ein erschwinglicher Ersatz für DRAM sein

- Liefert eine dramähnliche Leistung bei 4x die Kapazität und die Hälfte der Kosten

- Sandisk sagt, es wird erschwinglicher, wenn die Technologie reift

Bei seiner jüngsten Sitzung von Sandisk 2.0 Investor Day stellte der Flash Storage -Riese eine Reihe neuer SSDs vor, darunter ein 128 -TB -Rechenzentrumsmodell, und skizzierte seine ehrgeizige Roadmap für noch größere Laufwerke – eine 256 -TB -SSD im Jahr 2026, eine 512TB -SSD im Jahr 2027, und 2027 und 2027 und 2027 und 2026 und 2027 usw. Ein satte 1PB -Laufwerk erwartete einige Jahre später.

Sandisk ist bestrebt, jeden Investor -Wobbles zu beruhigen, folgt seiner Trennung von Western DigitalUnd abgesehen davon, dass die Strategie zur Steigerung der Renditen und der Margen diskutiert, nahm das Unternehmen auch die Wraps von seinem bahnbrechenden 3D-Matrix-Speicher, eine skalierbare Speichertechnologie, die Berichten zufolge die dramähnliche Leistung mit vierfachen Kapazitäten und der Hälfte der Kosten verspricht.

Sandisk hat den 3D-Matrixspeicher als erschwingliche Lösung als Reaktion auf das Ende des Mooreschen Gesetzes für DRAM positioniert, wo die Skalierung der Stagnation, eine erweiterte Rechendickerlücke und die steigenden Speicherkosten zu großen Herausforderungen geworden sind. Das Unternehmen sagt, dass seine skalierbare Gedächtnisarchitektur die “Speicherwand” durchbrechen und das Problem der Speicherkapazität und der Bandbreite, die darum kämpft, mit immer größeren Verarbeitungsanforderungen Schritt zu halten.

Kostengünstiger

Der 3D -Matrix -Gedächtnis von Sandisk wurde in Zusammenarbeit mit IMEC entwickelt und basiert auf einer dichten Array -Architektur mit einem neuartigen Speicher -Memory -Cell -Design und hält die Kompatibilität mit offenen Branchenstandards wie CXL auf.

Das Unternehmen behauptet, dass seine neue Speichertechnologie im Laufe der Zeit immer kosteneffizienter werden werde. Laut einem Graph, der Sandisk geteilt hat, erzielt der 3D -Matrixspeicher bis zum 6. Jahr im Jahr 6 im Vergleich zu DRAM über 50% Kosteneinsparungen pro Bit, wobei ein deutlich steilerer Rückgang von US -Dollar/GB zu einer günstigeren Alternative zu herkömmlichen DRAM -Lösungen ist.

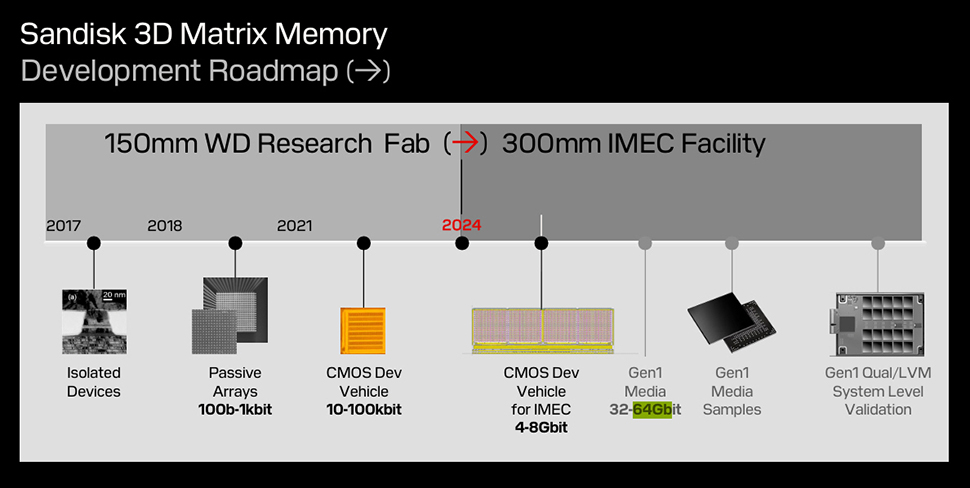

Die unten gezeigte Entwicklungs-Roadmap des Unternehmens beschreibt eine Reihe von Meilensteinen, wobei der Übergang von einem 150-mm-WD-Forschung FAB zu einer 300-mm-IMEC-Einrichtung im Jahr 2024 übergeht und den ersten bedeutenden Schritt der Technologie in Richtung großer Maßnahmen zur Produktion von Tech markiert.

Ab 2017 hat sich das Projekt von isolierten Geräten zu passiven Arrays zu CMOS -Entwicklungsfahrzeugen entwickelt. Gen1-Medienproben werden der nächste große Schritt sein, und diese werden voraussichtlich 32-64Gbit-Kapazitäten erreichen, obwohl es bisher keine Details zur Rohleistung gibt.